PowerLattice attracts investment from ex-Intel CEO Pat Gelsinger for its power-saving chiplet

PowerLattice raises $25M for its 50% power-saving chiplet, backed by former Intel CEO Pat Gelsinger, as demand for efficient AI computing surges.

As the world’s largest tech companies race to meet soaring AI demand, one problem keeps rising to the surface: a shortage of compute capacity. Training and running the massive AI models now powering today’s products requires huge data centres — and those data centres need unprecedented amounts of power. With energy consumption becoming a significant bottleneck, semiconductor companies are rapidly seeking breakthroughs in power efficiency.

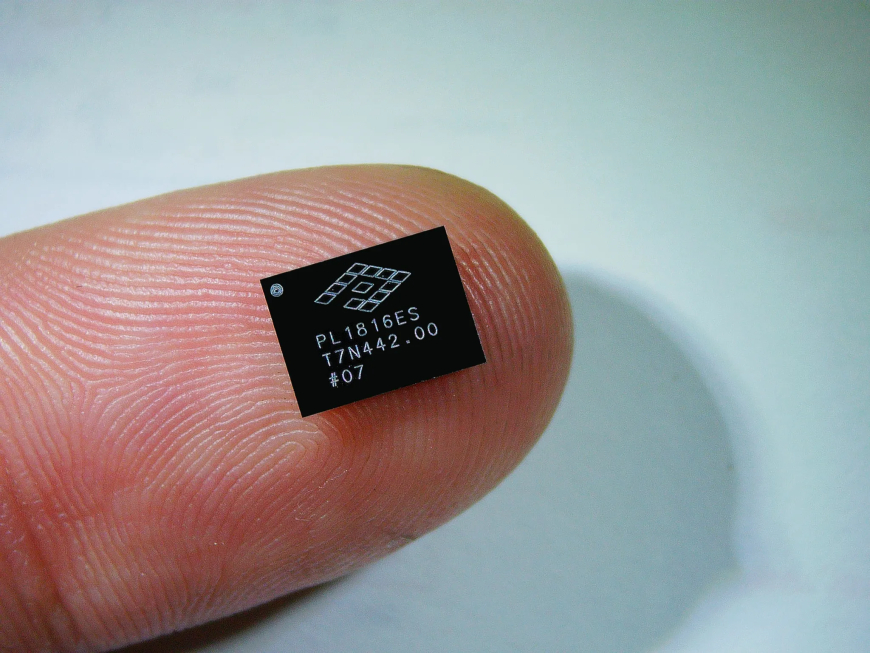

PowerLattice, a startup founded in 2023 by veteran engineers from Qualcomm, NUVIA, and Intel, believes it has one. The company claims to have developed a new power-delivery chiplet that can reduce a computer chip’s power consumption by more than 50%. On Monday, PowerLattice officially emerged from stealth, announcing a $25 million Series A round led by Playground Global and Celesta Capital, bringing the total funding to $31 million.

“This is the hard stuff: How do you get power into the device? There are very few teams and people that can do it,” said Pat Gelsinger, general partner at Playground Global. “We have assembled what I’d argue is the dream team of power delivery.”

Gelsinger, the former Intel CEO, is one of the semiconductor industry’s most influential figures, and his involvement is a significant endorsement of PowerLattice’s approach. He recalled that when CEODr. Peng Zou and the founding team pitched the company at Playground’s offices in March. They were so excited to meet him that they asked for a selfie, but the admiration quickly went both ways. Gelsinger said he walked away genuinely impressed by the technology.

PowerLattice’s concept sounds straightforward: move the power delivery system closer to the processor to reduce the energy lost during transmission. But executing this at the scale and performance required by today’s chips is far from simple.

Now two years into development, the startup has hit a significant milestone. Its first batch of chiplets is already being manufactured by TSMC, in partnership with an undisclosed company that is currently testing PowerLattice’s technology, according to Gelsinger.

The company plans to open its technology for broader customer testing in the first half of 2026. Its potential customer list reads like a who’s who of the semiconductor world — Nvidia, AMD, and Broadcom — along with specialised AI chip developers such as Cerberus, Grok, d-Matrix, and NextSilicon, the latter two of which are backed by Playground as well.

Even though many chipmakers have internal teams working on similar problems, Gelsinger believes PowerLattice’s approach will stand out.

“They may say, ‘I’m going to take some volume to this approach, some volume to my more traditional approach,’” he noted. “But we think our ability to capture meaningful share will quickly emerge.”

PowerLattice isn’t the only startup trying to solve chip-level power inefficiencies. Empower Semiconductor, which raised $140 million in a Series D led by Fidelity Management & Research Company in September, is also targeting this problem. But Gelsinger says PowerLattice’s more than 50% power-efficiency improvement is an “extraordinary” achievement — one he expects will attract significant future investment.

“The idea is bold, the benefits are large, and I expect others will be saying, ‘That’s a great idea. Let me try as well,’” Gelsinger added.

What's Your Reaction?

Like

0

Like

0

Dislike

0

Dislike

0

Love

0

Love

0

Funny

0

Funny

0

Angry

0

Angry

0

Sad

0

Sad

0

Wow

0

Wow

0